T R S - O S

What is TRS-OS? It is software providing services & resources to support execution of LSDOS 6.3.X / TRSDOS on platforms using Zilog's eZ80 processor series. LSDOS/TRSDOS is a popular operating system for Radio Shack 1970/80's microcomputer series known as TRS-80. TRSDOS was originally designed for Zilog's Z80 microprocessor. TRSDOS 6.x was designed to be device & hardware independent with focus on portable. It was ahead of its time like many other greats in microcomputer history. It was designed for hardware independence & portability. I have with some degree of fidelity enabled original OS & most apps to run on a processor up to 5000% faster than original Z80.

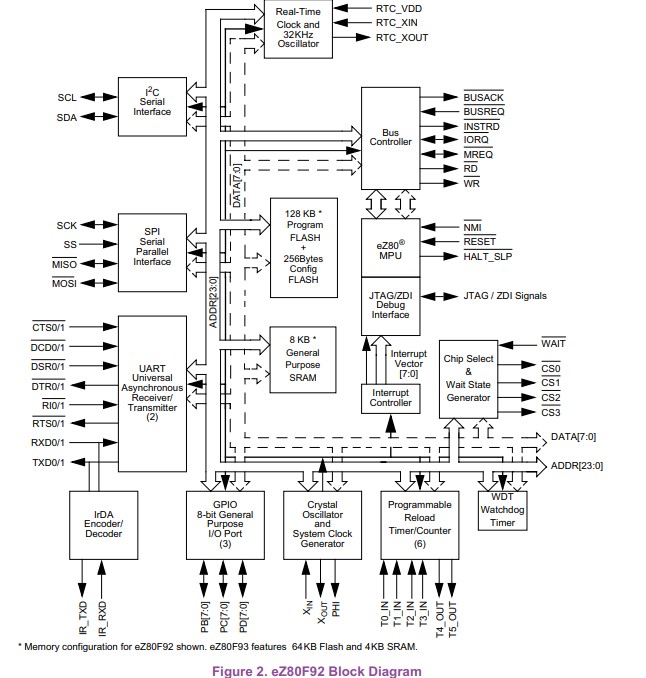

In addition of eZ80f91, TRS-OS supports eZ80f92. One load module self configures to either processor platform on boot.

What does TRS-OS stand for? TRS-OS stands for The Resource Sharing - Operating System. This is exactly what it does. It provides sharing facilities enabling modern eZ80 built in peripherals & devices to be shared with TRSDOS. In TRSDOS, these peripherals & devices will appear as closely as possible the devices they are simulating.

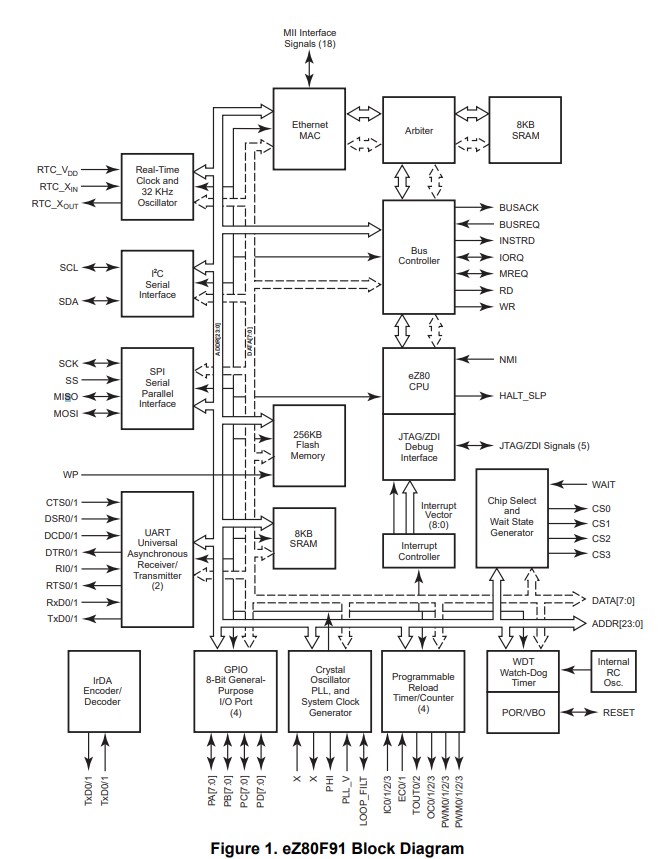

- What is a Zilog eZ80? Zilog’s eZ80 is Zilog’s solution for an embedded processor breaking 64k address barrier. eZ80 is backward binary compatible with Zilog’s famous Z80 processor. There are several versions of eZ80 available depending on job at hand (eZ80F91, F92, F93 etc). At this time discussions and specs will be limited to eZ80F91 Acclaim. Figure 1 below shows key features using block diagram.

Key features of eZ80F91 device include:

• Single-cycle instruction fetch, high-performance, pipelined eZ80® CPU core (referred as the CPU in this document).

• 10/100 BaseT ethernet media access controller with Media-Independent Interface (MII).

• 256 KB Flash memory.

• 16 KB SRAM (8 KB user and 8 KB Ethernet).

• Low-power features including SLEEP mode, HALT mode, and selective peripheral power-down control.

• Two Universal Asynchronous Receiver/Transmitter (UART) with independent Baud Rate Generators (BRG).

• Serial Peripheral Interface (SPI) with independent clock rate generator.

• I2C with independent clock rate generator.

• IrDA-compliant infrared encoder/decoder.

• Glueless external peripheral interface with 4 Chip Selects, individual Wait State generators, an external WAIT input pin—supports Z80-, Intel-, and Motorola-style buses.

• Fixed-priority vectored interrupts (both internal and external) and interrupt controller.

• Real-time clock with separate VDD pin for battery backup and selectable on-chip 32 kHz oscillator or external 50/60 Hz input.

• Four 16-bit Counter/Timers with prescalers and direct input/output drive.

• Watchdog Timer with internal oscillator clocking option.

• 32 bits of General-Purpose Input/Output (GPIO).

• On-Chip Instrumentation (OCI™) and Zilog Debug Interfaces (ZDI).

eZ80F91 Block diagram from Zilog.

Below is little brother, eZ80F92. Different speed and options.